The unique and growing capabilities present in modern reconfigurable computing platforms such as Field Programmable Gate Arrays (FPGAs) are attractive for efficient and fault-tolerant computations. Prime among these capabilities is Dynamic Partial Reconfiguration, which allows users to harness the high performance of hardware to achieve flexibility close to that of software.

However, certain challenges have kept these potentials from being effectively exploited in the field of reconfigurable computing. Some of the major challenges border around the lack of reliability, the lack of tool support, large reconfiguration time and application and system security. In addition, it has not been possible to effectively harness the potentials of such platforms without integrating external processors with them, leading to issues such as inefficient data sharing among the different processing elements in a heterogeneous system.

In order to alleviate these challenges, and especially to make reconfigurable platforms more attractive to application developers, our current research in this field seeks to develop an operating system support for heterogeneous systems comprising various processing elements, including FPGAs, GPUs, and conventional processors.

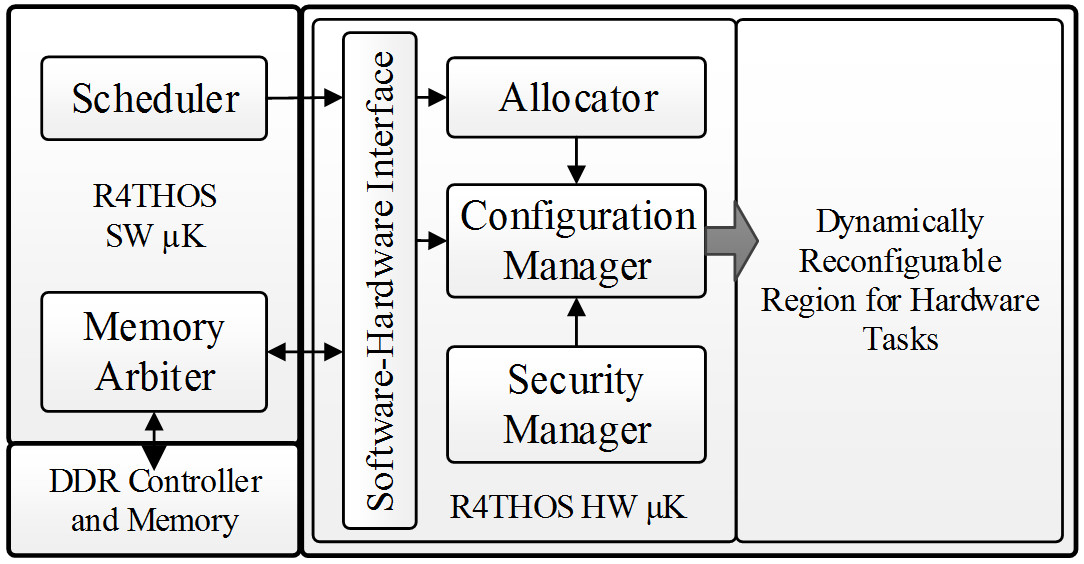

We take on a range of issues relating to the development of such operating systems solutions. This ranges from low-level algorithms for scheduling and allocation to manage the reconfigurable chip area, security and configuration management to high-level issues such as compiler support for applications in high-level languages and design optimization tools.

Shown below is a simplified initial block diagram of the key features of the operating system named R4THOS - Robust Reliable Reconfigurable Real-Time Heterogeneous Operating System.

Two key ongoing researches in the Reconfigurable Operating Systems research area are:

- HIgh Performance and Robust Multisensor Operating Systems

- Scheduling and Allocation for Embedded Reconfigurable Systems

- Fault Tolerant Reconfigurable Sensor Node for Deep-water Application

Present projects include:

- Fault-Tolerant Computing in Reconfigurable Operating System

- Allocation Algorithms for Heterogeneous Reconfigurable Operating System

- Configuration Management for Hardware Tasks (Circuits)

- Inter-Task Hardware Communication

- Software-Hardware Interfacing for Heterogeneous Task Processing

- Security in Reconfigurable Operating Systems

- Hardware Task Scheduling

Recent publications include:

- A. Adetomi, G. Enemali, and T. Arslan, ‘Enabling Dynamic Communication for Runtime Circuit Relocation’, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 1, pp. 142–155, Jan. 2020, doi: 10.1109/TVLSI.2019.2934927.

- A. Adetomi, G. Enemali, X. Iturbe, D. Keymeulen, and T. Arslan, ‘R3TOS-Based Integrated Modular Space Avionics for On-Board Real-Time Data Processing’, in 2018 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), Edinburgh, UK, Aug. 2018, pp. 1–8.

- A. Adetomi, G. Enemali, and T. Arslan, ‘Characterization of Clock Buffers for On-Chip Inter-Circuit Communication in Xilinx FPGAs’, in 2018 IEEE International Symposium on Circuits and Systems (ISCAS), May 2018, pp. 1–5, doi: 10.1109/ISCAS.2018.8351604.

- A. Adetomi, G. Enemali, and T. Arslan, "Towards an Efficient Intellectual Property Protection in Dynamically Reconfigurable FPGAs", in 2017 International Conference on Emerging Security Technologies (EST), 2017, pp. 150-156, 10.1109/EST.2017.8090415.

- A. Adetomi, G. Enemali, and T. Arslan, "Relocation-Aware Communication Network for Circuits on Xilinx FPGAs‘’, in 2017 International Conference on Field Programmable Logic and Applications (FPL), 2017, pp. 1-7, 10.23919/FPL.2017.8056818.

- G. Enemali, A. Adetomi, and T. Arslan, "A Placement Management Circuit for Efficient Realtime Hardware Reuse on FPGAs Targeting Reliable Autonomous Systems", in 50th IEEE International Symposium on Circuit and Systems (ISCAS 2017), 2017, pp. 2030 – 2033, 10.1109/ISCAS.2017.8050796

- A. Adetomi, G. Enemali, and T. Arslan, "A Fault-Tolerant ICAP Controller with a Selective-Area Soft Error Mitigation Engine", in 2017 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), 2017, pp. 192-199, 10.1109/AHS.2017.8046378.

- G. Enemali, A. Adetomi, and T. Arslan, "Expanding the Un-usable Area Strategy for Improved Utilization of Reconfigurable FPGAs", in 2017 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), 2017, 10.1109/AHS.2017.8046370.

- A. Adetomi, G. Enemali, and T. Arslan, "Relocating Encrypted Partial Bitstreams by Advance Task Address Loading", in 25th Annual IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM 2017), 2017, pp. 188–191, 10.1109/FCCM.2017.50.

- A. Adetomi, G. Enemali, and T. Arslan, "Clock Buffers, Nets, and Trees for On-Chip Communication: A Novel Network Access Technique in FPGAs", in 2017 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), 2017, pp. 219–222, 10.1109/IPDPSW.2017.156.

- G. Enemali, A. Adetomi, and T. Arslan, "FAReP: Fragmentation-Aware Replacement Policy for Task Reuse on Reconfigurable FPGAs", in 2017 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), 2017, pp. 202 – 206, 10.1109/IPDPSW.2017.153.